|

市场调查报告书

商品编码

1959328

晶片互连市场机会、成长要素、产业趋势分析及2026年至2035年预测Chiplet Interconnect Market Opportunity, Growth Drivers, Industry Trend Analysis, and Forecast 2026 - 2035 |

||||||

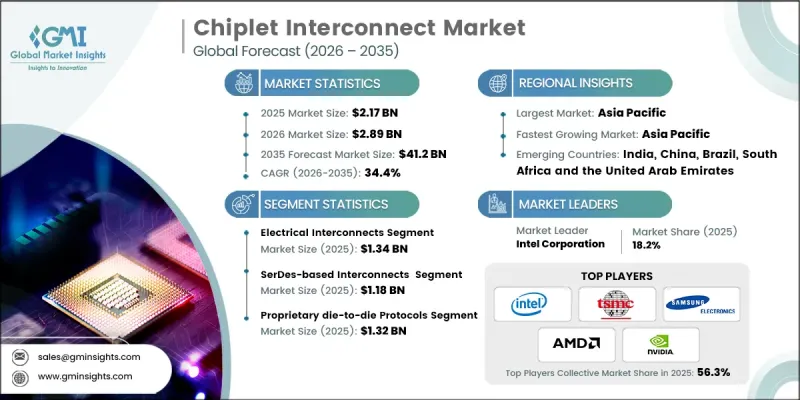

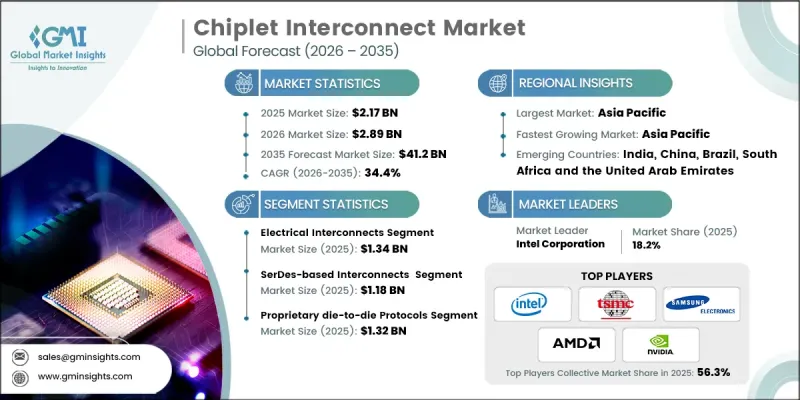

2025 年全球晶片互连市场价值为 21.7 亿美元,预计到 2035 年将达到 412 亿美元,复合年增长率为 34.4%。

市场扩张的驱动力来自对异质整合日益增长的需求、先进製程节点成本优化以及扩展人工智慧和高效能运算 (HPC) 工作负载的需求。晶片组架构实现了模组化设计的柔软性、提高了产量比率并降低了对单片式晶片的依赖,同时支援生态系统标准化和开放互连通讯协定。政府和产业项目正在推动先进封装和模组化晶片策略,以加速创新、增加晶片多样性并缩短复杂运算系统的上市时间。边缘设备、资料中心和企业运算平台正受益于晶片组,晶片组克服了人工智慧、高效能运算和伺服器应用中单晶片的局限性,可提供高频宽、低延迟和可扩展的效能。对设计工具、中介层技术和基板开发的策略性投资正在进一步加强产业对晶片组的应用。

| 市场范围 | |

|---|---|

| 开始年份 | 2025 |

| 预测年份 | 2026-2035 |

| 起始值 | 21.7亿美元 |

| 预测金额 | 412亿美元 |

| 复合年增长率 | 34.4% |

预计到2025年,电气互连市场规模将达到13.4亿美元。由于其可靠性、易整合性和与现有封装生态系统的兼容性,电气互连在晶片设计中仍然占据主导地位。它们尤其适用于人工智慧、高效能运算和伺服器处理器,其成熟的製造流程、广泛的代工厂支援和完善的设计基础设施使其能够以经济高效的方式扩展。製造商可以在资料中心、网路设备和企业运算系统中大规模部署电气互连,从而支援大规模部署。

预计到2025年,基于SerDes的互连市场规模将达到11.8亿美元,主要得益于其在多晶粒架构中实现的远距离、高速资料传输能力。 SerDes与UCIe和PCIe等业界标准的高度相容性使其成为高阶人工智慧、高效能运算和网路应用的理想选择。 SerDes整合可降低设计风险,加速技术普及,并实现与企业半导体平台的无缝部署。

预计到2025年,北美晶片互连市场份额将达到42.7%。该地区受益于强大的半导体生态系统、先进的研发能力以及对尖端封装技术的早期应用,这些技术能够实现人工智慧和高效能运算系统所必需的低延迟、高频宽互连。政府奖励、研究伙伴关係以及对中介层和基板技术的投资,进一步巩固了北美在异构整合、模组化晶片设计和稳健的半导体供应链方面的地位。

目录

第一章:调查方法和范围

第二章执行摘要

第三章业界考察

- 生态系分析

- 供应商情况

- 利润率

- 成本结构

- 每个阶段增加的价值

- 影响价值链的因素

- 中断

- 影响产业的因素

- 促进因素

- 对异质一体化的需求

- 先进节点的成本最佳化

- 扩展人工智慧和高效能运算工作负载

- 产量比率和设计柔软性

- 生态系标准化和开放互联

- 挑战与困难

- 缺乏普遍的互通性

- 热管理和功率管理限制

- 促进因素

- 成长潜力分析

- 监理情势

- 北美洲

- 欧洲

- 亚太地区

- 拉丁美洲

- 中东和非洲

- 波特的分析

- PESTEL 分析

- 科技与创新趋势

- 当前技术趋势

- 新兴技术

- 新兴经营模式

- 合规要求

- 供应链韧性

- 地缘政治分析

第四章 竞争情势

- 介绍

- 企业市占率分析

- 按地区

- 北美洲

- 欧洲

- 亚太地区

- 拉丁美洲

- 中东和非洲

- 市场集中度分析

- 按地区

- 主要企业的竞争标竿分析

- 产品系列比较

- 产品线的广度

- 科技

- 创新

- 区域扩张比较

- 全球扩张分析

- 服务网路覆盖

- 按地区分類的市场渗透率

- 竞争定位矩阵

- 领导企业

- 受让人

- 追踪者

- 小众玩家

- 战略展望矩阵

- 产品系列比较

- 2022-2025 年重大发展

- 併购

- 合作伙伴关係和合资企业

- 技术进步

- 扩张和投资策略

- 永续发展倡议

- 数位转型计划

- 新兴/Start-Ups竞争对手的发展趋势

第五章 市场估计与预测:依互连类型划分,2022-2035年

- 电气互连

- 光连接模组

第六章 市场估算与预测:依讯号传输法划分,2022-2035年

- 基于SerDes的互连

- 基于平行互连

第七章 市场估计与预测:依通讯协定模型划分,2022-2035年

- 主要趋势

- 开放标准通讯协定

- UCIe

- BoW(一束电线)

- OpenHBI

- 专有的晶粒间通讯协定

第八章 市场估算与预测:依互连IP层划分,2022-2035年

- 主要趋势

- 物理层 (PHY) IP

- SerDes PHY IP

- 并行PHY IP

- 光物理层 (PHY) IP

- 控制器和通讯协定层 IP

- 通讯协定控制器 IP

- 连结和流量控制 IP

- 相干引擎 IP

- 通讯协定适配器和桥接 IP

第九章 市场估价与预测:依互连硬体划分,2022-2035年

- 主要趋势

- 硅中介层

- 嵌入式硅胶桥

- 有机中介层和扇出RDL

第十章 市场估价与预测:依最终用途划分,2022-2035年

- 主要趋势

- 高效能运算(HPC)

- 人工智慧/机器学习加速器

- 资料中心云端基础设施

- 用于网路和交换的专用积体电路

- 汽车电子

- 消费计算

- 工业和边缘运算

- 其他的

第十一章 市场估价与预测:按地区划分,2022-2035年

- 北美洲

- 我们

- 加拿大

- 欧洲

- 德国

- 英国

- 法国

- 西班牙

- 义大利

- 荷兰

- 亚太地区

- 中国

- 印度

- 日本

- 澳洲

- 韩国

- 拉丁美洲

- 巴西

- 墨西哥

- 阿根廷

- 中东和非洲

- 沙乌地阿拉伯

- 南非

- 阿拉伯聯合大公国

第十二章:公司简介

- 主要企业

- Advanced Micro Devices(AMD)

- Intel Corporation

- NVIDIA Corporation

- Broadcom Inc.

- Samsung Electronics

- 按地区分類的主要企业

- 北美洲

- Marvell Technology

- Cadence Design Systems

- Synopsys

- 欧洲

- Alphawave Semi

- Siemens EDA(Mentor Graphics)

- 亚太地区

- Taiwan Semiconductor Manufacturing Company(TSMC)

- Amkor Technology

- ASE Technology Holding

- 北美洲

- 小众/颠覆性公司

- Ayar Labs

- Rambus Inc.

The Global Chiplet Interconnect Market was valued at USD 2.17 billion in 2025 and is estimated to grow at a CAGR of 34.4% to reach USD 41.2 billion by 2035.

The market is expanding due to the rising demand for heterogeneous integration, cost optimization at advanced process nodes, and the need to scale AI and high-performance computing (HPC) workloads. Chiplet architecture provides modular design flexibility, improved yield, and reduced reliance on monolithic chips while supporting ecosystem standardization and open interconnect protocols. Governments and industrial programs are promoting advanced packaging and modular chip strategies to accelerate innovation, increase silicon diversity, and reduce time-to-market for complex computing systems. Edge devices, data centers, and enterprise computing platforms benefit from chiplets that deliver high bandwidth, low latency, and scalable performance, addressing the limitations of standalone chips in AI, HPC, and server applications. Industry adoption is further strengthened by strategic investments in design tools, interposer technology, and substrate development.

| Market Scope | |

|---|---|

| Start Year | 2025 |

| Forecast Year | 2026-2035 |

| Start Value | $2.17 Billion |

| Forecast Value | $41.2 Billion |

| CAGR | 34.4% |

The electrical interconnects segment accounted for USD 1.34 billion in 2025. Electrical interconnects remain dominant in chiplet designs due to their reliability, ease of integration, and compatibility with existing packaging ecosystems. They are particularly suited for AI, HPC, and server processors, where mature manufacturing processes, widespread foundry support, and established design infrastructure make scaling cost-effective. Manufacturers can deploy electrical interconnects at scale in data centers, networking equipment, and enterprise computing systems, supporting high-volume adoption.

The SerDes-based interconnects segment reached USD 1.18 billion in 2025, driven by their capability to transmit high-speed data over long distances across multi-die architectures. These interconnects are ideal for advanced AI, HPC, and networking applications due to strong alignment with industry standards such as UCIe and PCIe. SerDes integration reduces design risks, accelerates adoption, and enables seamless deployment in enterprise semiconductor platforms.

North America Chiplet Interconnect Market held a 42.7% share in 2025. The region benefits from a robust semiconductor ecosystem, advanced R&D, and early access to cutting-edge packaging technologies that enable low-latency, high-bandwidth interconnects essential for AI and HPC systems. Government incentives, research partnerships, and investment in interposer and substrate technologies further strengthen North America's position in heterogeneous integration, modular chip design, and resilient semiconductor supply chains.

Leading companies in the Global Chiplet Interconnect Market include Intel Corporation, NVIDIA Corporation, Advanced Micro Devices (AMD), Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Broadcom Inc., Marvell Technology, Synopsys, Cadence Design Systems, Siemens EDA (Mentor Graphics), Alphawave Semi, Rambus Inc., Ayar Labs, ASE Technology Holding, and Amkor Technology. Key strategies adopted by companies to strengthen their position in the Global Chiplet Interconnect Market include investing heavily in R&D to develop high-bandwidth, low-latency interconnects optimized for AI, HPC, and enterprise applications. Firms are forming strategic alliances with semiconductor foundries, design tool providers, and cloud computing companies to ensure seamless ecosystem integration. Companies focus on adopting open standards such as UCIe to enhance modularity and reduce interoperability risks. They are expanding global manufacturing capabilities, including interposer and substrate production, to meet regional demand.

Table of Contents

Chapter 1 Methodology and Scope

- 1.1 Market scope and definition

- 1.2 Research design

- 1.2.1 Research approach

- 1.2.2 Data collection methods

- 1.3 Data mining sources

- 1.3.1 Global

- 1.3.2 Regional/Country

- 1.4 Base estimates and calculations

- 1.4.1 Base year calculation

- 1.4.2 Key trends for market estimation

- 1.5 Primary research and validation

- 1.5.1 Primary sources

- 1.6 Forecast model

- 1.7 Research assumptions and limitations

Chapter 2 Executive Summary

- 2.1 Industry 360° synopsis

- 2.2 Key market trends

- 2.2.1 Interconnect type trends

- 2.2.2 Signalling architecture trends

- 2.2.3 Protocol model trends

- 2.2.4 Interconnect IP layer trends

- 2.2.5 Interconnect-enabling hardware

- 2.2.6 End-use trends

- 2.2.7 Regional trends

- 2.3 TAM Analysis, 2026-2035 (USD Million)

- 2.4 CXO perspectives: Strategic imperatives

- 2.4.1 Executive decision points

- 2.4.2 Critical success factors

- 2.5 Future outlook and strategic recommendations

Chapter 3 Industry Insights

- 3.1 Industry ecosystem analysis

- 3.1.1 Supplier landscape

- 3.1.2 Profit margin

- 3.1.3 Cost structure

- 3.1.4 Value addition at each stage

- 3.1.5 Factor affecting the value chain

- 3.1.6 Disruptions

- 3.2 Industry impact forces

- 3.2.1 Growth drivers

- 3.2.1.1 Heterogeneous integration demand

- 3.2.1.2 Advanced node cost optimization

- 3.2.1.3 Ai and hpc workload scaling

- 3.2.1.4 Yield improvement and design flexibility

- 3.2.1.5 Ecosystem standardization and open interconnects

- 3.2.2 Pitfalls and challenges

- 3.2.2.1 Lack of universal interoperability

- 3.2.2.2 Thermal and power management constraints

- 3.2.1 Growth drivers

- 3.3 Growth potential analysis

- 3.4 Regulatory landscape

- 3.4.1 North America

- 3.4.2 Europe

- 3.4.3 Asia Pacific

- 3.4.4 Latin America

- 3.4.5 Middle East & Africa

- 3.5 Porter’s analysis

- 3.6 PESTEL analysis

- 3.7 Technology and Innovation landscape

- 3.7.1 Current technological trends

- 3.7.2 Emerging technologies

- 3.8 Emerging Business Models

- 3.9 Compliance Requirements

- 3.10 Supply Chain Resilience

- 3.11 Geopolitical Analysis

Chapter 4 Competitive Landscape, 2025

- 4.1 Introduction

- 4.2 Company market share analysis

- 4.2.1 By region

- 4.2.1.1 North America

- 4.2.1.2 Europe

- 4.2.1.3 Asia Pacific

- 4.2.1.4 Latin America

- 4.2.1.5 Middle East & Africa

- 4.2.2 Market concentration analysis

- 4.2.1 By region

- 4.3 Competitive benchmarking of key players

- 4.3.1 Product portfolio comparison

- 4.3.1.1 Product range breadth

- 4.3.1.2 Technology

- 4.3.1.3 Innovation

- 4.3.2 Geographic presence comparison

- 4.3.2.1 Global footprint analysis

- 4.3.2.2 Service network coverage

- 4.3.2.3 Market penetration by region

- 4.3.3 Competitive positioning matrix

- 4.3.3.1 Leaders

- 4.3.3.2 Challengers

- 4.3.3.3 Followers

- 4.3.3.4 Niche players

- 4.3.4 Strategic outlook matrix

- 4.3.1 Product portfolio comparison

- 4.4 Key developments, 2022-2025

- 4.4.1 Mergers and acquisitions

- 4.4.2 Partnerships and collaborations

- 4.4.3 Technological advancements

- 4.4.4 Expansion and investment strategies

- 4.4.5 Sustainability initiatives

- 4.4.6 Digital transformation initiatives

- 4.5 Emerging/ startup competitors landscape

Chapter 5 Market Estimates and Forecast, By Interconnect Type, 2022 - 2035 (USD Million)

- 5.1 Key trends

- 5.2 Electrical interconnects

- 5.3 Optical interconnects

Chapter 6 Market Estimates and Forecast, By Signaling Architecture, 2022 - 2035 (USD Million)

- 6.1 Key trends

- 6.2 SerDes-based interconnects

- 6.3 Parallel-based interconnects

Chapter 7 Market Estimates and Forecast, By Protocol Model, 2022 - 2035 (USD Million)

- 7.1 Key Trends

- 7.2 Open standard protocols

- 7.2.1 UCIe

- 7.2.2 BoW (Bunch of Wires)

- 7.2.3 OpenHBI

- 7.3 Proprietary die-to-die protocols

Chapter 8 Market Estimates and Forecast, By Interconnect IP Layer, 2022 - 2035 (USD Million)

- 8.1 Key Trends

- 8.2 Physical Layer (PHY) IP

- 8.2.1 SerDes PHY IP

- 8.2.2 Parallel PHY IP

- 8.2.3 Optical PHY IP

- 8.3 Controller & Protocol Layer IP

- 8.3.1 Protocol controller IP

- 8.3.2 Link & flow control IP

- 8.3.3 Coherency engine IP

- 8.3.4 Protocol adapter & bridging IP

Chapter 9 Market Estimates and Forecast, By Interconnect-Enabling Hardware, 2022 - 2035 (USD Million)

- 9.1 Key Trends

- 9.2 Silicon interposers

- 9.3 Embedded silicon bridges

- 9.4 Organic interposers & Fan-Out RDL

Chapter 10 Market Estimates and Forecast, By End-use, 2022 - 2035 (USD Million)

- 10.1 Key Trends

- 10.2 High-performance computing (HPC)

- 10.3 Artificial intelligence / machine learning accelerators

- 10.4 Data center & cloud infrastructure

- 10.5 Networking & switching ASICs

- 10.6 Automotive electronics

- 10.7 Consumer computing

- 10.8 Industrial & edge computing

- 10.9 Others

Chapter 11 Market Estimates and Forecast, By Region, 2022 - 2035 (USD Million)

- 11.1 Key trends

- 11.2 North America

- 11.2.1 U.S.

- 11.2.2 Canada

- 11.3 Europe

- 11.3.1 Germany

- 11.3.2 UK

- 11.3.3 France

- 11.3.4 Spain

- 11.3.5 Italy

- 11.3.6 Netherlands

- 11.4 Asia Pacific

- 11.4.1 China

- 11.4.2 India

- 11.4.3 Japan

- 11.4.4 Australia

- 11.4.5 South Korea

- 11.5 Latin America

- 11.5.1 Brazil

- 11.5.2 Mexico

- 11.5.3 Argentina

- 11.6 Middle East and Africa

- 11.6.1 Saudi Arabia

- 11.6.2 South Africa

- 11.6.3 UAE

Chapter 12 Company Profiles

- 12.1 Global Key Players

- 12.1.1 Advanced Micro Devices (AMD)

- 12.1.2 Intel Corporation

- 12.1.3 NVIDIA Corporation

- 12.1.4 Broadcom Inc.

- 12.1.5 Samsung Electronics

- 12.2 Regional Key Players

- 12.2.1 North America

- 12.2.1.1 Marvell Technology

- 12.2.1.2 Cadence Design Systems

- 12.2.1.3 Synopsys

- 12.2.2 Europe

- 12.2.2.1 Alphawave Semi

- 12.2.2.2 Siemens EDA (Mentor Graphics)

- 12.2.3 Asia Pacific

- 12.2.3.1 Taiwan Semiconductor Manufacturing Company (TSMC)

- 12.2.3.2 Amkor Technology

- 12.2.3.3 ASE Technology Holding

- 12.2.1 North America

- 12.3 Niche / Disruptors

- 12.3.1 Ayar Labs

- 12.3.2 Rambus Inc.