|

市场调查报告书

商品编码

1687980

扇出型封装:市场占有率分析、产业趋势与统计、成长预测(2025-2030)Fan Out Packaging - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2025 - 2030) |

||||||

※ 本网页内容可能与最新版本有所差异。详细情况请与我们联繫。

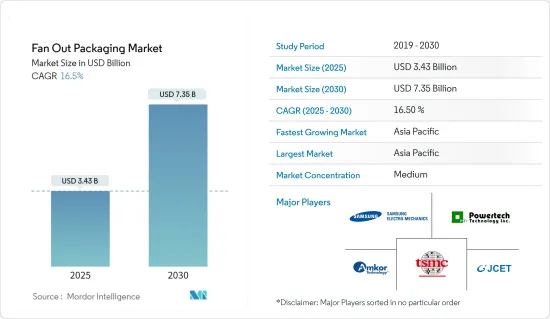

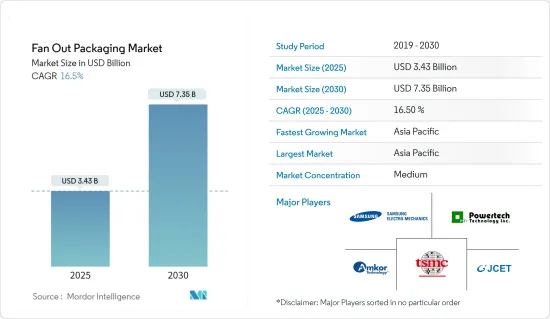

扇出型封装市场规模在 2025 年预估为 34.3 亿美元,预计到 2030 年将达到 73.5 亿美元,在市场预估和预测期(2025-2030 年)内复合年增长率为 16.5%。

该市场的扩张受到半导体技术的进步和各个领域快速增长的需求的推动。

主要亮点

- 扇出晶圆层次电子构装(FOWLP) 在智慧型手机等安装面积非常宝贵的设备中的应用日益广泛,因为人们需要高性能、节能的薄型小封装。此外,现代智慧型手机平均包含 5-7 个晶圆级封装(尤其是扇出型),而且这个数字预计还会继续成长。这是因为它正在逐步取代传统的封装上封装(PoP)逻辑记忆体解决方案。

- 此外,人工智慧和机器学习在各个领域的应用日益广泛,导致市场对高效能运算的采用也不断增加。由于 UHD 扇出技术在云端、5G、自动驾驶汽车和 AI 晶片中的应用,预计该技术将在预测期内引领封装趋势。

- 韩国半导体产业持续努力改进3D TSV(硅穿孔电极)、封装、FoWLP(扇出型晶圆级封装)以及FoPLP(扇出型面板级封装)技术,使其更有效地提升半导体性能和整合度。

- 2021 年 12 月,Nepes Laue 宣布利用 Deca 的 M 系列扇出技术成功生产了世界上第一个大型 600mm x 600mm 面板级封装 (PLP)。该公司表示,其扇出型面板级封装 (FOPLP) 生产线在第三季度通过了客户认证,实现了稳定的产量比率并开始全面量产。

- 韩国企业传统上依赖海外公司提供这些系统,因此 KOSTEK 预计未来将出现显着的进口替代效应。临时晶圆键合机和解键合技术可用于扇出型封装製程。

- 由于货物流动的限制导致半导体供应链严重中断,COVID-19 疫情导致半导体封装市场成长放缓。 2020 年第一季,COVID-19 导致半导体供应商和分销通路客户的存量基准较低。预计冠状病毒疫情将对市场产生长期影响。

扇出型封装市场趋势

高密度扇出占很大份额

- 高密度扇出针对中阶高阶应用,每平方毫米有 6 到 12 个 I/O,线宽/间距范围从 15/15μm 到 5/5μm。高密度扇出型封装已成为满足行动电话封装外形规格和效能要求的热门方法。此技术的主要组成部分是重分布层(RDL)金属和巨柱镀层。

- 台积电的 InFO 技术是高密度扇出型技术最突出的例子之一。此技术针对的是引脚数较高的应用,例如应用处理器 (AP)。该公司计划将FO-WLP领域扩展到inFO-Antenna-in-Package(AiP)和inFO-on-Substrate等技术。这些封装用于汽车、伺服器和智慧型手机。苹果是这项新技术的早期采用者之一,并将其应用于 2016 年底发布的 iPhone 7 的 A10 应用处理器中。

- 有鑑于这些优势,2021 年 12 月,高通和联发科均考虑采用扇出型 PoP 生产自己的旗舰智慧型手机应用处理器,效仿苹果使用台积电的 InFO_PoP 技术封装其 iPhone 晶片。

- 此外,预计预测期内半导体市场的成长和高密度扇出型封装解决方案的发展将推动市场成长。例如,2021年7月,全球领先的多电路製造商和技术解决方案供应商灿电科技透露,正式推出针对XDFOI晶片的全系列超高密度扇出型封装选项。旨在为晶片异构整合提供高成本效率、高密度连接、高整合度、高可靠性的解决方案。

- 先进封装也正在高密度扇出晶圆层次电子构装(FOWLP) 製造方法中进行。正在开发解决方案以缩小晶片尺寸/高度并降低製造成本,同时提高可靠性、能源效率、设备速度和多功能整合。例如,SPTS Technologies 为领先的半导体封装公司提供多种等电浆蚀刻和沈积製程技术,用于高密度扇出型晶圆级封装等先进封装方案。

- 此外,高密度扇出型 (HDFO) 封装可以透过晶圆级加工製造能力以及使用通模互连(例如高铜 (Cu) 柱和通孔 (TPV))和先进的覆晶构装技术创建 3D 结构的能力来满足这些小型化需求。

台湾占很大市场份额

- 台湾是主要半导体製造公司的所在地,推动了对先进封装(尤其是 PLP)的需求。据政府智库科学技术国际战略中心称,台湾的产出预计将在 2021 年成长 25.9%,达到 1,470 亿美元。

- 据半导体行业协会(SIA)称,亚太地区占全球半导体销售额的50%以上。这将为台湾供应商提供向越来越多的半导体应用供应FOWLP的机会。

- 台湾多数业者正扩大扇出型封装产能,预期将增加出口量并有助于国内市场发展。例如,近期宣布重返晶圆代工产业的英特尔,正同时投资35亿美元在美国新墨西哥州兴建半导体封装厂,预计于2022年下半年投入营运。

- 此外,2021年6月,纯半导体后端处理(OAST)公司ASE开始投资先进封装设备,以解决半导体供需短缺问题。该公司正从韩美半导体购买大量用于WLP和PLP製程的半导体製造设备,以加速其扩张业务。

- 此外,第五代(5G)无线通讯和高效能运算的市场发展使得製造商能够开发新技术。例如,作为高密度扇出型领域的唯一领导者,台积电计划将FO-WLP领域扩展到inFO-Antenna-in-Package(AiP)和inFO-on-Substrate(oS)等技术。

扇出型封装产业概览

市场中等分散,参与者人数众多。全球扇出型封装市场的主要企业包括台湾半导体製造股份有限公司、江苏长江电子科技股份有限公司、安靠科技股份有限公司、三星电机股份有限公司和力成科技股份有限公司。这些公司正致力于产品创新、併购等发展,以扩大市场占有率。

- 2021 年 11 月-半导体封装与测试服务供应商 Amkor Technology, Inc. 宣布有意在越南北宁兴建一座智慧工厂。该工厂的初始阶段将专注于为世界领先的半导体和电子产品製造商提供先进的系统级封装(SiP)组装和测试服务。

- 2021 年 2 月-三星代工厂已向亚利桑那州、纽约州和德克萨斯州的当局提交文件,寻求在美国建立先进的半导体製造工厂。该工厂将建在德克萨斯州奥斯汀附近,预计投资超过 170 亿美元,创造 1,800 个就业机会。预计将于 2023 年第四季运作。

其他福利:

- Excel 格式的市场预测 (ME) 表

- 3 个月的分析师支持

目录

第 1 章 简介

- 研究假设和市场定义

- 研究范围

第二章调查方法

第三章执行摘要

第四章 市场洞察

- 市场概况

- 产业吸引力-波特五力分析

- 供应商的议价能力

- 买家的议价能力

- 新进入者的威胁

- 竞争对手之间的竞争

- 替代品的威胁

- COVID-19 市场影响

第五章 市场动态

- 市场驱动因素

- 高效能运算与 5G 无线网路腾飞

- 市场限制

- 与生产相关的製造成本问题

- FOPLP 的市场机会

- COVID-19 市场影响

第六章 市场细分

- 按类型

- 核心扇出

- 高密度扇出

- 超高密度扇出

- 依承运商类型

- 200 mm

- 300 mm

- 控制板

- 按经营模式

- OSAT

- 铸造厂

- IDM

- 按地区

- 台湾

- 中国

- 美国

- 韩国

- 日本

- 欧洲

第七章 扇出型封装厂商排名分析

第八章 竞争格局

- 公司简介

- Taiwan Semiconductor Manufacturing Company Limited

- Jiangsu Changjiang Electronics Tech Co.

- Samsung Electro-Mechanics

- Powertech Technology Inc.

- Amkor Technology Inc.

- Advanced Semiconductor Engineering Inc

- Nepes Corporation

第九章投资分析

第 10 章:未来展望

The Fan Out Packaging Market size is estimated at USD 3.43 billion in 2025, and is expected to reach USD 7.35 billion by 2030, at a CAGR of 16.5% during the forecast period (2025-2030).

The expansion of this market is being driven by technological advancements in semiconductor-based technologies and rapidly expanding demand in various sectors.

Key Highlights

- Fan-out wafer level packaging (FOWLP) finds its increased application in footprint-sensitive devices such as smartphones due to the requirement of high-performing, energy-efficient thin- and small-form-factor packages. Further, on average, five to seven wafer-level packages (especially fan-out) can be found in modern smartphones, and the numbers are expected to increase in the future. This is because they are gradually replacing the more traditional package-on-package (PoP) memory-on-logic solutions.

- Moreover, the increasing application of artificial intelligence and machine learning in various fields has increased the installation of high-performance computing in the market. UHD fan-out technology is expected to be applied to the cloud, 5G, autonomous cars, and AI chips and will lead the packaging trend during the forecast period.

- South Korea's semiconductor industry is continuing to put in efforts to improve and make 3D TSV (Through-silicon via), packaging and FoWLP (Fan-out Wafer-Level Packaging), and FoPLP (Fan-out Panel-Level Packaging) technologies more effective to raise the performance of semiconductors and the degree of integration.

- In December 2021, Nepes Laweh corporation announced the successful production of the world's first 600 mm x 600 mm large Panel Level Packaging (PLP) using Deca's M-Series fan-out technologies. The Fan-out-Panel Level Packaging (FOPLP) line passed customer certification in the third quarter, established a consistent yield, and commenced full-scale mass production, according to the business.

- Because South Korean companies depended on foreign companies for these systems in the past, KOSTEK is expecting a huge import substitution effect in the future. Its temporary wafer bonder and debonding techniques can be used during a fan-out packaging process.

- With the outbreak of COVID-19, the semiconductor packaging market witnessed a decline in growth due to restrictions on the movement of goods and severe disruptions in the semiconductor supply chain. In Q1 2020, COVID-19 caused low inventory levels for clients of semiconductor vendors and distribution channels. The market is expected to witness a long-term impact due to the coronavirus outbreak.

Fan Out Packaging Market Trends

High-Density Fan-Out to Hold a Significant Share

- Targeted for mid-range to high-end apps, high-density fan-out has between 6 to 12 I/Os per mm2 and between 15/15 μm to 5/5 μm line/space. High-density fan-out packaging gained popularity to address the form factor and performance requirements for mobile phone packaging. Key building blocks for this technology comprise redistribution layer (RDL) metal and mega pillar plating.

- TSMC's InFO technology is one of the most notable examples of high-density fan-out. This technology targets higher pin count applications, such as application processors (AP). The company plans to extend its FO-WLP segment into technologies like inFO-Antenna-in-Package (AiP) and inFO-on-Substrate. These packages are used in automobiles, servers, and smartphones. Apple was one of the early adopters of this new technology, which used it in the A10 application processor of the iPhone 7, introduced in late 2016.

- Owing to such benefits, in December 2021, Qualcomm and MediaTek both considered adopting fan-out PoP in the production of their flagship smartphone application processors, following in the footsteps of Apple utilizing TSMC's InFO_PoP technology to package its iPhone chips.

- Furthermore, semiconductor market growth along with development in high-density fan-out packaging solutions is expected to propel market growth over the forecast period. For instance, in July 2021, Changdian Technology, the world's premier combined circuit manufacturer and technology solution provider, revealed the official introduction of the entire line of very high-density fan-out packaging options for XDFOI chips, that are intended to deliver cost-effective, high-density connectivity, high-integration, and high-reliability solutions for chip heterogeneous integration.

- Advancements are also made in the fabrication method of manufacturing High-Density Fan-Out Wafer Level Packaging (FOWLP). Solutions are being developed to reduce chip size/height and lower production costs while improving reliability, energy efficiency, device speed, and multi-function integration. For instance, SPTS Technologies offers multiple plasma etch and deposition process technologies to leading semiconductor packaging companies for advanced packaging schemes such as that of high-density fan-out wafer-level packaging.

- Moreover, high-density fan-out (HDFO) packages can address these needs of miniaturization by fabrication capabilities of wafer-level processing coupled with its ability to create 3D structures using through-mold interconnects such as tall copper (Cu) pillars and through package vias (TPVs) and advanced flip chip packaging technologies.

Taiwan to Hold a Significant Share in the Market

- Taiwan houses some of the major semiconductor manufacturing companies which are fueling the demand for advanced semiconductor packaging, especially in PLPs. According to a government think tank, Science and Technology International Strategy Center, Taiwan's output was expected to grow by 25.9% in 2021 to USD 147 billion.

- According to the Semiconductor Industry Association (SIA), Asia-Pacific generates more than 50% of revenue for global semiconductor sales; this, in turn, provides Taiwanese vendors with an opportunity to supply FOWLP for increased semiconductor applications.

- Most of the companies in the country are expanding their production capacity of Fan-out packaging, which is further expected to increase exports and help develop the local market. For instance, Intel, which recently announced its return to the foundry industry, will simultaneously invest USD 3.5 billion in New Mexico to construct a semiconductor packaging factory that will begin operations in the second half of 2022.

- Further, in June 2021, ASE, a pure semiconductor post-processing (OAST), started investing in advanced packaging facilities in response to the supply and demand shortage of semiconductors. It is accelerating the expansion by purchasing a large amount of semiconductor manufacturing equipment for WLP and PLP processes from HANMI Semiconductor.

- Also, the growing market for fifth-generation (5G) wireless communication and high-performance computing has enabled manufacturers to develop newer technologies. For instance, as a sole leader in the High-Density Fan-out segment, TSMC is planning to extend its FO-WLP segment into technologies like inFO-Antenna-in-Package (AiP) and inFO-on-Substrate (oS).

Fan Out Packaging Industry Overview

The market is moderately fragmented, with the presence of numerous players. Some of the major players operating in the global fan-out packaging market include Taiwan Semiconductor Manufacturing Company Limited, Jiangsu Changjiang Electronics Tech Co., Amkor Technology Inc., Samsung Electro-Mechanics, and Powertech Technology Inc., among others. These players indulge in product innovation, mergers, and acquisitions, among other developments, in order to increase market share.

- November 2021 - Amkor Technology, Inc., a semiconductor packing and test service supplier, stated that it intends to construct an intelligent factory in Bac Ninh, Vietnam. The proposed factory's initial phase will concentrate on offering Advanced System in Package (SiP) assembling and testing services to the world's premier semiconductor and electronics manufacturing businesses.

- February 2021 - Samsung Foundry has filed documents with authorities in Arizona, New York, and Texas seeking to build a leading-edge semiconductor manufacturing facility in the USA. The potential fab near Austin, Texas, is expected to cost over USD 17 billion and create 1,800 jobs. It is expected to go online by the fourth quarter of 2023.

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET INSIGHTS

- 4.1 Market Overview

- 4.2 Industry Attractiveness - Porter's Five Forces Analysis

- 4.2.1 Bargaining Power of Suppliers

- 4.2.2 Bargaining Power of Buyers

- 4.2.3 Threat of New Entrants

- 4.2.4 Intensity of Competitive Rivalry

- 4.2.5 Threat of Substitute Products

- 4.3 Impact of COVID-19 on the Market

5 MARKET DYNAMICS

- 5.1 Market Drivers

- 5.1.1 The Proliferation of 5G Wireless Networking Along with High-performance Computing

- 5.2 Market Restraints

- 5.2.1 Manufacturing And Cost Challenges Associated with Production

- 5.3 Market Opportunities for FOPLP

- 5.4 Impact of COVID-19 on the market

6 MARKET SEGMENTATION

- 6.1 By Type

- 6.1.1 Core Fan-Out

- 6.1.2 High-Density Fan-Out

- 6.1.3 Ultra High-density Fan Out

- 6.2 By Carrier Type

- 6.2.1 200 mm

- 6.2.2 300 mm

- 6.2.3 Panel

- 6.3 By Business Model

- 6.3.1 OSAT

- 6.3.2 Foundary

- 6.3.3 IDM

- 6.4 Geography

- 6.4.1 Taiwan

- 6.4.2 China

- 6.4.3 United States

- 6.4.4 South Korea

- 6.4.5 Japan

- 6.4.6 Europe

7 FAN-OUT PACKAGING VENDOR RANKING ANALYSIS

8 COMPETITIVE LANDSCAPE

- 8.1 Company Profiles

- 8.1.1 Taiwan Semiconductor Manufacturing Company Limited

- 8.1.2 Jiangsu Changjiang Electronics Tech Co.

- 8.1.3 Samsung Electro-Mechanics

- 8.1.4 Powertech Technology Inc.

- 8.1.5 Amkor Technology Inc.

- 8.1.6 Advanced Semiconductor Engineering Inc

- 8.1.7 Nepes Corporation