|

市场调查报告书

商品编码

1940817

系统晶片(SoC):市场份额分析、行业趋势和统计数据、成长预测(2026-2031 年)System On Chip (SoC) - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031) |

||||||

※ 本网页内容可能与最新版本有所差异。详细情况请与我们联繫。

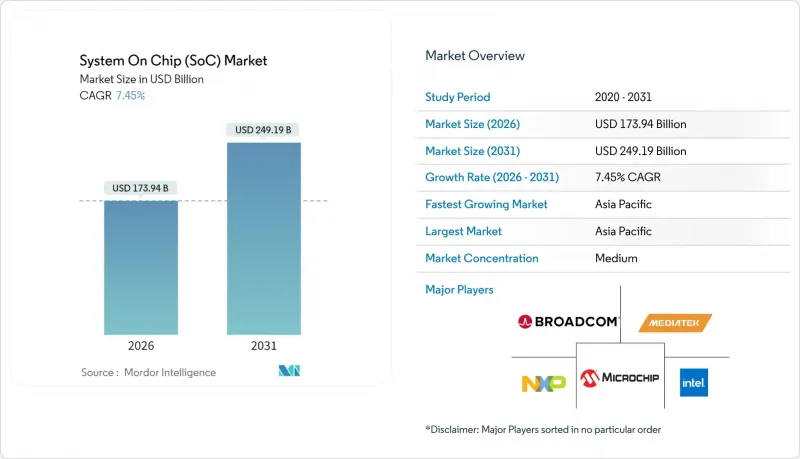

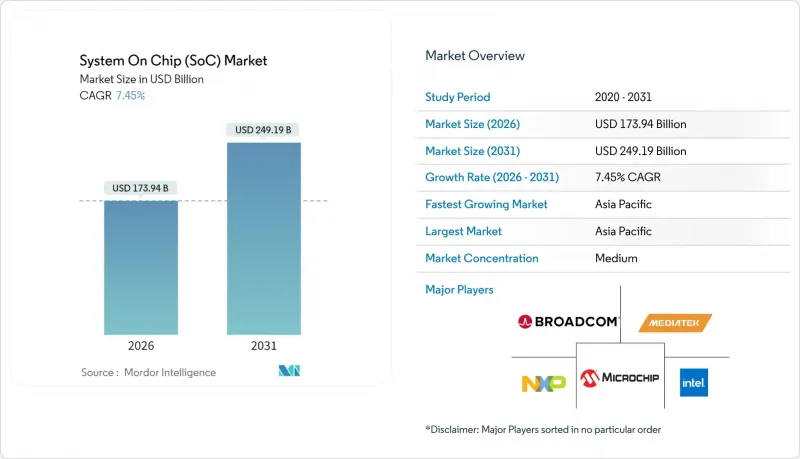

预计系统晶片(SoC) 市场将从 2025 年的 1,618.8 亿美元成长到 2026 年的 1,739.4 亿美元,到 2031 年将达到 2,491.9 亿美元,2026 年至 2031 年的复合年增长率为 7.45%。

智慧型手机更新换代速度放缓,但边缘原生AI推理和5G客户端设备的快速普及抵消了这一影响,从而实现了稳定的出货量和平均晶粒尺寸的增加。一级汽车製造商将数十个控制单元整合到集中式运算域中,推动了对多核心、具备ASIL-D等级的SoC的需求。超大规模资料中心业者持续以自主设计取代现成晶片,扩大了先进封装供应商的潜在市场。美国、日本和欧盟的区域晶圆厂激励政策支持了产能扩张,降低了供应链风险,并促进了在地化设计策略的实施。

全球系统晶片(SoC) 市场趋势与洞察

对5G相容设备的需求激增

首批独立组网的5G网路导致上行链路预算更加紧张,基频也更加复杂,迫使智慧型手机OEM厂商在调变解调器子系统中整合AI调优引擎。高通骁龙8 Elite将Release 17级调变解调器与45 TOPS神经网路引擎结合,相比上一代产品,每瓦效能提升了45%。联发科天莹9400采用了类似的层级架构,加速了2025年初发布的高阶智慧型手机的在线连续影片增强功能。工业路由器的配套模组也采用了类似的整合方式,无需透过云端即可在智慧工厂单元内实现亚毫秒操作。因此,智慧型手机和工业网关的更新换代推动了系统晶片(SoC)市场近期营收的激增。

物联网和人工智慧边缘运算的快速普及

分散式推理工作负载的兴起迫使设计人员将通用核心、DSP 和神经网路加速器整合到单一晶粒上。 EdgeCortix 的 SAKURA-II 晶片功耗低于 10 瓦,却能提供 40 TOPS 的运算能力,已被用于装配线上零件检测的工业相机所采用。智慧城市整合商透过改造交通号誌控制柜,加装微型伺服器,在传输元元资料之前对视讯串流进行本地压缩,从而将回程传输减少了 80%。这种架构转变提高了每个节点的硅含量,同时缩短了设计週期,使得异构/融合 SoC系统晶片(SoC) 市场中成长最快的细分领域。

5纳米以下製程设计与掩模成本飙升

2024年底,台积电2nm製程的掩模组成本将超过每片晶圆3万美元,比3nm製程高出50%。这导致复杂SoC计划的总预算飙升至1亿美元。只有少数无厂半导体公司能够承担如此高昂的费用,迫使许多设计人员继续沿用成熟的製程节点。这限制了晶片的功能集成,并减缓了领先EDA供应商的潜在市场成长。

细分市场分析

到2025年,数位SoC装置将占总收入的52.45%,这反映了它们在智慧型手机和通用运算领域的普及。设计人员在不同层级重复使用可扩展的IP库,从而降低了成本曲线,并加快了衍生产品的上市速度。然而,基于晶片堆迭技术的出现对单晶片数位SoC的主导地位构成了首个结构性挑战。将CPU、GPU、NPU和专用加速器整合在单一中介层上的异质/融合SoC预计将以9.7%的复合年增长率成长,从而蚕食传统数位SoC的市场份额。混合讯号SoC在感测器融合和电源管理(例如电池BMS控制器)的交叉领域仍将发挥重要作用。射频/连接SoC将受益于Wi-Fi 7和5G RedCap的日益普及,而类比晶片将为动力传动系统和工业驱动提供支援。因此,SoC 市场正处于转型期,研发投入正从增量研发转向模组化、特定领域的混合型晶片,同时保持其在数位领域的量化优势。

这种架构重组也导致了代工厂配置的变化。纯数位晶片的流片集中在运转率极高的7/6nm製程线上,而早期的异构原型则将5nm逻辑晶片与16nm模拟晶片组合晶粒,并整合到台积电的SoIC封装流程中。这种分离保护了模拟IP免受超细鳍片宽度缩小带来的性能损失,并降低了风险。供应商透过通用晶片互连高速(UCIe)规范推动标准化,旨在促进2026年后多源晶片市场的形成。随着互通性的成熟,系统晶片(SoC)市场预计将加速产品类型的更新换代,缩短设计週期,并扩大从晶粒到封装的价值创造。

到2025年,家用电子电器占总收入的45.58%,这主要得益于行动电话、穿戴式装置和AR眼镜的12-18个月週期性更新换代。内容成长主要来自支援生成式AI相机功能的大规模ISP丛集。然而,汽车产业超越通讯基础设施,成为成长最快的产业,到2031年复合年增长率将达到13.85%。这项转变主要由软体定义车辆蓝图驱动,该路线图将感知处理、区域控制和资讯娱乐工作负载集中在有限的车辆运算节点上。一级供应商开始签署多年半导体供应协议,从而降低了分配风险,并为SoC製造商提供了前所未有的需求可视性。工业和物联网领域保持了稳定的个位数成长,这得益于现有设施的维修,这些改造在PLC上实施了预测性维护模型。

在医疗领域,体内连续血糖监测仪获得监管部门批准,推动了对整合无线功能的超低功耗生物医学SoC的需求。资料中心的需求随着AWS等超大规模资料中心业者采用其自主研发的Graviton4 CPU而转变,通用伺服器CPU的潜在市场规模(TAM)有所缩小,但同时也推动了对机架式共封装光控制器的需求。电信基础设施收入受惠于5G Advanced基频升级,但由于开放式无线接取网路(RAN)定价,利润率有所下降。整体而言,系统晶片(SoC)市场依靠汽车和边缘人工智慧物联网订单来缓解消费性行动电话的週期性波动,凸显了各垂直产业需求结构的多样性。

系统晶片(SoC) 市场按产品类型(数位 SoC、类比 SoC、混合讯号 SoC、射频/连接 SoC 等)、终端用户产业(家用电子电器、通讯基础设施、汽车等)、製程节点(28nm 及以上、16/14nm、10/8nm、7/6

区域分析

亚太地区预计到2025年将占全球营收的54.20%,并将持续保持领先成长,到2031年复合年增长率将达到9.75%。中国的「小巨人」扶持计画已扶持了200多家国内SoCStart-Ups,这些企业专注于从低轨道卫星数据机到汽车光达讯号处理器等垂直细分市场。韩国整合装置製造商(IDM)透过使用自主生产的DRAM和HBM将记忆体和运算模组捆绑在一起,增强了生态系统的凝聚力。台湾晶圆代工厂保持了其製程技术的领先地位,并于2025年第二季交付了首批采用2nm环栅製程的风险晶圆。同时,日本晶圆厂正专注于为电动车驱动逆变器生产宽能带隙功率SoC。

在北美,英特尔在俄亥俄州投资200亿美元,以及位于新墨西哥州的新封装厂(于2025年4月开始试营运),都为该地区带来了强劲的成长动力。 AWS从2024年7月开始在美国五个可用区部署基于Graviton 4架构的实例,并报告指出Web层效能提升了30%。这形成了一个晶片飞轮效应,加速了国内晶片的设计週期。儘管政府出口管制政策的调整限制了与中国的双边贸易,但强劲的云端运算和国防费用帮助该地区维持了较高的个位数复合年增长率。

欧洲已将重心转向汽车硅技术领域的卓越发展。德国汽车製造商与英飞凌和意法半导体签署了多代供应协议,以确保ADAS(高级驾驶辅助系统)运算能力;欧盟晶片法案承诺投入430亿欧元(约479亿美元),力争到2030年将区域产能翻倍。法国和义大利联合投资建造了晶圆层次电子构装线,确保了工业4.0部署所需的供应自主性。这些发展表明,儘管亚太地区仍保持着规模优势,系统晶片(SoC)市场正朝着兼顾规模和韧性的三方供应结构演变。

其他福利:

- Excel格式的市场预测(ME)表

- 3个月的分析师支持

目录

第一章 引言

- 研究假设和市场定义

- 调查范围

第二章调查方法

第三章执行摘要

第四章 市场情势

- 市场概览

- 市场驱动因素

- 对5G相容设备的需求激增

- 物联网和人工智慧边缘运算的快速普及

- 汽车产业向集中式电子电气架构的过渡

- 补贴以扩大本地晶圆厂规模

- 基于晶片组的异质整合技术发展势头强劲

- 边缘原生AI模型推理的需求

- 市场限制

- 5纳米以下製程设计与掩模成本飙升

- 出口管制使供应链变得脆弱

- 晶片组互通性标准尚不成熟

- 高阶SoC的热密度限制

- 宏观经济因素的影响

- 价值链分析

- 监管环境

- 技术展望

- 波特五力分析

- 供应商的议价能力

- 买方的议价能力

- 新进入者的威胁

- 替代品的威胁

- 竞争对手之间的竞争

- Chiplet采用与去中心化趋势分析

第五章 市场规模与成长预测

- 依产品类型

- 数位SoC

- 模拟SoC

- 混合讯号SoC

- 射频/连接SoC

- 异构/融合SoC

- 按最终用户行业划分

- 家用电子电器

- 通讯基础设施

- 车

- 计算和资料中心

- 工业和物联网

- 医疗保健和医疗设备

- 按行程节点

- 28奈米或更大

- 16/14 nm

- 10/8 nm

- 7/6 nm

- 5/4/3 nm

- 2 nm 或更小/3-DIC

- 透过使用

- 智慧型手机和平板电脑

- 边缘人工智慧和物联网设备

- 伺服器和资料中心

- 汽车ADAS/资讯娱乐系统

- 工业自动化

- 穿戴式装置和智慧家居

- 按地区

- 北美洲

- 我们

- 加拿大

- 南美洲

- 巴西

- 南美洲其他地区

- 欧洲

- 德国

- 法国

- 英国

- 义大利

- 西班牙

- 俄罗斯

- 其他欧洲地区

- 亚太地区

- 中国

- 日本

- 韩国

- 台湾

- 印度

- 亚太其他地区

- 中东和非洲

- 中东

- 沙乌地阿拉伯

- 阿拉伯聯合大公国

- 土耳其

- 其他中东地区

- 非洲

- 南非

- 奈及利亚

- 其他非洲地区

- 中东

- 北美洲

第六章 竞争情势

- 市场集中度

- 策略趋势

- 市占率分析

- 公司简介

- Advanced Micro Devices Inc.

- Apple Inc.

- Arm Holdings plc

- Broadcom Inc.

- Rockchip Electronics Co., Ltd.

- Google LLC(Tensor SoC)

- HiSilicon Technologies Co., Ltd.

- Infineon Technologies AG

- Intel Corporation

- Marvell Technology Inc.

- MediaTek Inc.

- Microchip Technology Inc.

- Nvidia Corporation

- NXP Semiconductors NV

- Qualcomm Technologies Inc.

- Realtek Semiconductor Corp.

- Renesas Electronics Corporation

- Samsung Electronics Co., Ltd.(System LSI)

- SiFive Inc.

- Silicon Labs Inc.

- STMicroelectronics NV

- Taiwan Semiconductor Manufacturing Company Limited

- Texas Instruments Incorporated

- Allwinner Technology Co., Ltd.

- UNISOC Technologies Co., Ltd.

第七章 市场机会与未来展望

The system-on-chip market is expected to grow from USD 161.88 billion in 2025 to USD 173.94 billion in 2026 and is forecast to reach USD 249.19 billion by 2031 at 7.45% CAGR over 2026-2031.

Softer smartphone refresh cycles were offset by rapid adoption of edge-native AI inference and 5G client devices, keeping unit volumes stable and average die sizes larger. Tier-one automotive OEMs consolidated dozens of control units into centralized compute domains, lifting demand for multicore, ASIL-D capable SoCs. Hyperscalers continued to displace merchant silicon with in-house designs, widening the addressable opportunity for advanced packaging providers. Regional fab incentives in the United States, Japan, and the European Union funded capacity that tempered supply-chain risk and encouraged localized design-for-manufacture strategies.

Global System On Chip (SoC) Market Trends and Insights

Soaring Demand for 5G-Enabled Devices

The first wave of standalone 5G networks brought tighter uplink budgets and higher baseband complexity, prompting smartphone OEMs to embed AI tuning engines inside the modem subsystem. Qualcomm's Snapdragon 8 Elite coupled a Release 17-class modem with a 45 TOPS neural engine that lifted performance per watt by 45% versus its predecessor. MediaTek's Dimensity 9400 adopted a similar hierarchy, accelerating in-line video enhancement for premium handsets launched in early 2025. Companion modules targeting industrial routers replicated this integration, allowing sub-millisecond actuation in smart-factory cells without cloud round-trips. Consequently, handset and industrial gateway refreshes amplified the near-term revenue pulse across the system-on-chip market.

Rapid IoT and AI-Edge Proliferation

Distributed inference workloads pushed designers to blend general-purpose cores, DSPs, and neural accelerators on a single die. EdgeCortix's SAKURA-II delivered 40 TOPS at sub-10-watt draw for industrial cameras that inspect parts in line. Smart-city integrators retrofitted traffic-signal cabinets with microservers that compress video streams locally before dispatching metadata, slashing backhaul by 80%. The architectural pivot increased silicon content per node while shortening design cycles, which in turn elevated heterogeneous/fusion SoCs as the fastest growing slice of the system on chip market.

Escalating Sub-5 nm Design and Mask Costs

Mask-set expenses for TSMC's 2 nm node surpassed USD 30,000 per wafer in late 2024, 50% higher than 3 nm, and drove total project budgets for complex SoCs toward USD 100 million. Only a handful of fabless houses could underwrite such outlays, forcing the long-tail of designers onto mature nodes, limiting feature integration and flattening TAM growth for bleeding-edge EDA vendors.

Other drivers and restraints analyzed in the detailed report include:

- Automotive Shift to Centralized E/E Architectures

- Subsidy-Fuelled Regional Fab Build-Out

- Export-Control Driven Supply-Chain Fragility

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

Digital SoC devices held 52.45% of 2025 revenue, reflecting their ubiquity in smartphones and general computing. Designers reused scalable IP libraries across tiers, smoothing cost curves and enabling rapid derivative launches. However, the arrival of chiplet-based stacking tolls the first structural challenge to monolithic digital supremacy. Heterogeneous/fusion SoCs-splicing CPU, GPU, NPU, and specialty accelerators on a single interposer-logged a 9.7% CAGR outlook, siphoning share from legacy digital formats. Mixed-signal variants remained pivotal where sensor fusion and power management intersected, such as in battery BMS controllers. RF/connectivity SoCs capitalized on expanded Wi-Fi 7 and 5G RedCap rollouts, while analog-centric devices anchored powertrain and industrial drive channels. The result is a transitional phase where the system-on-chip market preserves digital volume leadership yet directs incremental R&D to modular, domain-specific hybrids.

The architectural reshuffle also changed the foundry mix. Pure digital tape-outs gravitated to high utilization 7/6 nm lines, whereas early heterogeneous prototypes paired 5 nm logic dies with 16 nm analogue chiplets, nesting under TSMC's SoIC packaging flow. This partitioning lowered risk by sheltering analog IP from ultra-thin fin-width shrink penalties. Vendors emphasized standardization through the Universal Chiplet Interconnect Express (UCIe) specification, aiming to unleash a multi-sourced chiplet marketplace after 2026. As interoperability matures, the system-on-chip market is slated to witness an accelerated product-type turnover, compressing design cycles and amplifying die-to-package value capture.

Consumer electronics commanded 45.58% revenue in 2025 as handsets, wearables, and AR glasses refreshed on predictable 12-to-18-month cadences. Content gains came from larger ISP clusters that supported generative AI camera features. Yet, automotive overtook communications infrastructure as the fastest-growing sector, charting a 13.85% CAGR through 2031. The shift stemmed from software-defined vehicle roadmaps that centralize perception, domain control, and infotainment workloads on a limited number of vehicle compute nodes. Tier-ones began locking multi-year silicon supply agreements, curbing allocation risk and granting SoC houses unmatched demand visibility. The industrial and IoT segment maintained steady single-digit expansion, aided by brownfield retrofits that layered predictive-maintenance models atop PLCs.

In healthcare, regulatory clearances for in-body continuous-glucose monitors boosted volumes of ultra-low-power biomedical SoCs with integrated radios. Data-center demand evolved as hyperscalers such as AWS adopted internally developed Graviton4 CPUs, eroding merchant server-CPU TAM yet spurring co-packaged optics controllers inside racks. Communications infrastructure revenue benefited from 5G Advanced baseband upgrades, but margins compressed due to open-RAN pricing. Altogether, the system-on-chip market leaned on automotive and edge-AI IoT orders to cushion cyclicality in consumer handsets, showcasing its diversified demand mosaic across industries.

System On Chip Market is Segmented by Product Type (Digital SoC, Analog SoC, Mixed-Signal SoC, RF/Connectivity SoC, and More), End-User Industry (Consumer Electronics, Communications Infrastructure, Automotive, and More), Process Node (>=28 Nm, 16/14 Nm, 10/8 Nm, 7/6 Nm, and More), Application (Smartphones and Tablets, Edge-AI and IoT Devices, Servers and Data Centers, Automotive ADAS/Infotainment, and More), and Geography.

Geography Analysis

Asia-Pacific held 54.20% revenue in 2025 and continued to outpace all regions with a 9.75% CAGR to 2031. China's "Little Giant" subsidy track funded over 200 domestic SoC startups, each targeting vertical niches from low-orbit satellite modems to automotive lidar-signal processors. South Korean IDMs leveraged captive DRAM plus HBM production to bundle memory with compute tiles, tightening ecosystem stickiness. Taiwan's foundry corridor maintained process leadership, shipping the first risk wafers on 2 nm gate-all-around in Q2 2025, while Japanese fabs specialized in wide-bandgap power SoCs for EV traction inverters.

North America benefited from USD 20 billion of Intel investment in Ohio and a new packaging plant in New Mexico that entered pilot runs in April 2025. AWS rolled Graviton4-based instances across five U.S. availability zones after July 2024 and reported a 30% web-tier performance uplift, establishing a silicon flywheel that accelerates domestic design cycles. Government export-control updates did constrain bilateral trade with China, yet robust cloud and defense spending preserved a high single-digit CAGR for the region.

Europe pivoted around automotive silicon excellence. German OEMs locked multi-generational supply accords with Infineon and STMicroelectronics to secure ADAS compute, while the EU Chips Act committed EUR 43 billion (USD 47.9 billion) to double regional output capacity by 2030. France and Italy co-financed wafer-level packing lines for 3-DIC modules tailored to industrial automation systems, ensuring supply autonomy for Industry 4.0 rollouts. Collectively, these dynamics indicate that while Asia-Pacific retains numeric leadership, the system-on-chip market is evolving into a tri-polar supply landscape that balances resilience with scale.

- Advanced Micro Devices Inc.

- Apple Inc.

- Arm Holdings plc

- Broadcom Inc.

- Rockchip Electronics Co., Ltd.

- Google LLC (Tensor SoC)

- HiSilicon Technologies Co., Ltd.

- Infineon Technologies AG

- Intel Corporation

- Marvell Technology Inc.

- MediaTek Inc.

- Microchip Technology Inc.

- Nvidia Corporation

- NXP Semiconductors N.V.

- Qualcomm Technologies Inc.

- Realtek Semiconductor Corp.

- Renesas Electronics Corporation

- Samsung Electronics Co., Ltd. (System LSI)

- SiFive Inc.

- Silicon Labs Inc.

- STMicroelectronics N.V.

- Taiwan Semiconductor Manufacturing Company Limited

- Texas Instruments Incorporated

- Allwinner Technology Co., Ltd.

- UNISOC Technologies Co., Ltd.

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET LANDSCAPE

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 Soaring demand for 5G-enabled devices

- 4.2.2 Rapid IoT and AI-edge proliferation

- 4.2.3 Automotive shift to centralized E/E architectures

- 4.2.4 Subsidy-fuelled regional fab build-out

- 4.2.5 Chiplet-based heterogeneous integration momentum

- 4.2.6 Edge-native AI model inference needs

- 4.3 Market Restraints

- 4.3.1 Escalating <5 nm design and mask costs

- 4.3.2 Export-control driven supply-chain fragility

- 4.3.3 Immature chiplet interoperability standards

- 4.3.4 Thermal-density limits in high-end SoCs

- 4.4 Impact of Macroeconomic Factors

- 4.5 Value Chain Analysis

- 4.6 Regulatory Landscape

- 4.7 Technological Outlook

- 4.8 Porter's Five Forces Analysis

- 4.8.1 Bargaining Power of Suppliers

- 4.8.2 Bargaining Power of Buyers

- 4.8.3 Threat of New Entrants

- 4.8.4 Threat of Substitutes

- 4.8.5 Intensity of Competitive Rivalry

- 4.9 Chiplet Adoption and Disaggregation Trend Analysis

5 MARKET SIZE AND GROWTH FORECASTS (VALUE)

- 5.1 By Product Type

- 5.1.1 Digital SoC

- 5.1.2 Analog SoC

- 5.1.3 Mixed-signal SoC

- 5.1.4 RF / Connectivity SoC

- 5.1.5 Heterogeneous / Fusion SoC

- 5.2 By End-user Industry

- 5.2.1 Consumer Electronics

- 5.2.2 Communications Infrastructure

- 5.2.3 Automotive

- 5.2.4 Computing and Data Center

- 5.2.5 Industrial and IoT

- 5.2.6 Healthcare and Medical Devices

- 5.3 By Process Node

- 5.3.1 >=28 nm

- 5.3.2 16/14 nm

- 5.3.3 10/8 nm

- 5.3.4 7/6 nm

- 5.3.5 5/4/3 nm

- 5.3.6 2 nm and below / 3-DIC

- 5.4 By Application

- 5.4.1 Smartphones and Tablets

- 5.4.2 Edge-AI and IoT Devices

- 5.4.3 Servers and Data Centers

- 5.4.4 Automotive ADAS/Infotainment

- 5.4.5 Industrial Automation

- 5.4.6 Wearables and Smart Home

- 5.5 By Geography

- 5.5.1 North America

- 5.5.1.1 United States

- 5.5.1.2 Canada

- 5.5.2 South America

- 5.5.2.1 Brazil

- 5.5.2.2 Rest of South America

- 5.5.3 Europe

- 5.5.3.1 Germany

- 5.5.3.2 France

- 5.5.3.3 United Kingdom

- 5.5.3.4 Italy

- 5.5.3.5 Spain

- 5.5.3.6 Russia

- 5.5.3.7 Rest of Europe

- 5.5.4 Asia-Pacific

- 5.5.4.1 China

- 5.5.4.2 Japan

- 5.5.4.3 South Korea

- 5.5.4.4 Taiwan

- 5.5.4.5 India

- 5.5.4.6 Rest of Asia-Pacific

- 5.5.5 Middle East and Africa

- 5.5.5.1 Middle East

- 5.5.5.1.1 Saudi Arabia

- 5.5.5.1.2 United Arab Emirates

- 5.5.5.1.3 Turkey

- 5.5.5.1.4 Rest of Middle East

- 5.5.5.2 Africa

- 5.5.5.2.1 South Africa

- 5.5.5.2.2 Nigeria

- 5.5.5.2.3 Rest of Africa

- 5.5.5.1 Middle East

- 5.5.1 North America

6 COMPETITIVE LANDSCAPE

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Market Share Analysis

- 6.4 Company Profiles (includes Global-level Overview, Market-level Overview, Core Segments, Financials as available, Strategic Information, Market Rank/Share, Products and Services, Recent Developments)

- 6.4.1 Advanced Micro Devices Inc.

- 6.4.2 Apple Inc.

- 6.4.3 Arm Holdings plc

- 6.4.4 Broadcom Inc.

- 6.4.5 Rockchip Electronics Co., Ltd.

- 6.4.6 Google LLC (Tensor SoC)

- 6.4.7 HiSilicon Technologies Co., Ltd.

- 6.4.8 Infineon Technologies AG

- 6.4.9 Intel Corporation

- 6.4.10 Marvell Technology Inc.

- 6.4.11 MediaTek Inc.

- 6.4.12 Microchip Technology Inc.

- 6.4.13 Nvidia Corporation

- 6.4.14 NXP Semiconductors N.V.

- 6.4.15 Qualcomm Technologies Inc.

- 6.4.16 Realtek Semiconductor Corp.

- 6.4.17 Renesas Electronics Corporation

- 6.4.18 Samsung Electronics Co., Ltd. (System LSI)

- 6.4.19 SiFive Inc.

- 6.4.20 Silicon Labs Inc.

- 6.4.21 STMicroelectronics N.V.

- 6.4.22 Taiwan Semiconductor Manufacturing Company Limited

- 6.4.23 Texas Instruments Incorporated

- 6.4.24 Allwinner Technology Co., Ltd.

- 6.4.25 UNISOC Technologies Co., Ltd.

7 MARKET OPPORTUNITIES AND FUTURE OUTLOOK

- 7.1 White-space and Unmet-need Assessment